7551 JJ200 F43 V.2

# UNIVERSIDAD CATÓLICA ANDRÉS BELLO FACULTAD DE INGENIERÍA ESCUELA DE INGENIERÍA INFORMÁTICA

# Diseño y Construcción de un set de Realidad Virtual ANEXOS

#### TRABAJO ESPECIAL DE GRADO

presentado ante la

UNIVERSIDAD CATÓLICA ANDRÉS BELLO

como parte de los requisitos para optar al título de

INGENIERO EN INFORMÁTICA

REALIZADO POR

Dennis Federico

PROFESOR GUIA

Carlos Magurno

**FECHA**

20 de Noviembre del 2005

# UNIVERSIDAD CATÓLICA ANDRÉS BELLO FACULTAD DE INGENIERÍA ESCUELA DE INGENIERÍA INFORMÁTICA

### Diseño y Construcción de un set de Realidad Virtual **ANEXOS**

Este Jurado; una vez realizado el examen del presente trabajo ha evaluado su contenido con el resultado: 20 puntos - MENCIÓN HONORIFICA y

JURADO EXAMINADOR

Firma: Nombre: ASSAF YAMIN Nombre: Ramon Poras 6. Firma: Nombre: Carlo

REALIZADO POR

Dennis Federico

PROFESOR GUIA

Carlos Magurno

**FECHA**

20 de Noviembre del 2005

### INDICE DE ANEXOS.

0

| 1. Funcionamiento y construcción de los giroscopios de Analog Devices 2     |

|-----------------------------------------------------------------------------|

| 2. Características técnicas del Microcontrolador PIC 18f4550 5              |

| 3. Módulo USB del Microcontrolador PIC 18f4550                              |

| 4. Resumen del protocolo USB por Microchip                                  |

| 5. Registros del convertidor ADC del Microcontrolador PIC 18f4550 28        |

| 6. Tiempos de adquisición del convertidor ADC del PIC 18f4550 33            |

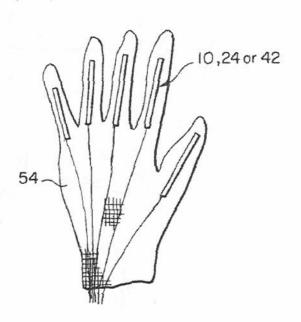

| 7. Flexor óptico de Zimmerman, Patente 4,542,291                            |

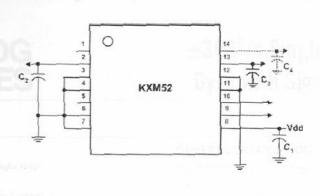

| 8. Hoja técnica de los acelerómetros Kionix serie KXM52                     |

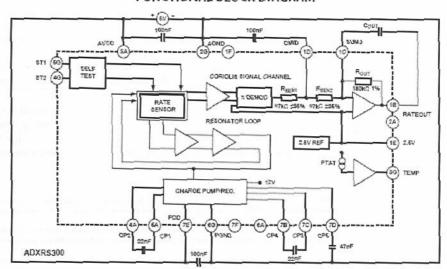

| 9. Hoja técnica del giroscopio ADXR300 de Analog Devices                    |

| 10. Descriptores Guante y Dispositivo de Rastreo Inercial en el firmware 45 |

| 11. Descriptores del dispositivo de rastreo mecánico en el firmware 49      |

| 12. Javadoc tesis.USB.DLLWrapper (Funcionalidad de la librería USB) 51      |

| 13. Ejemplos de uso del API                                                 |

| 14. Diagrama de clases del API                                              |

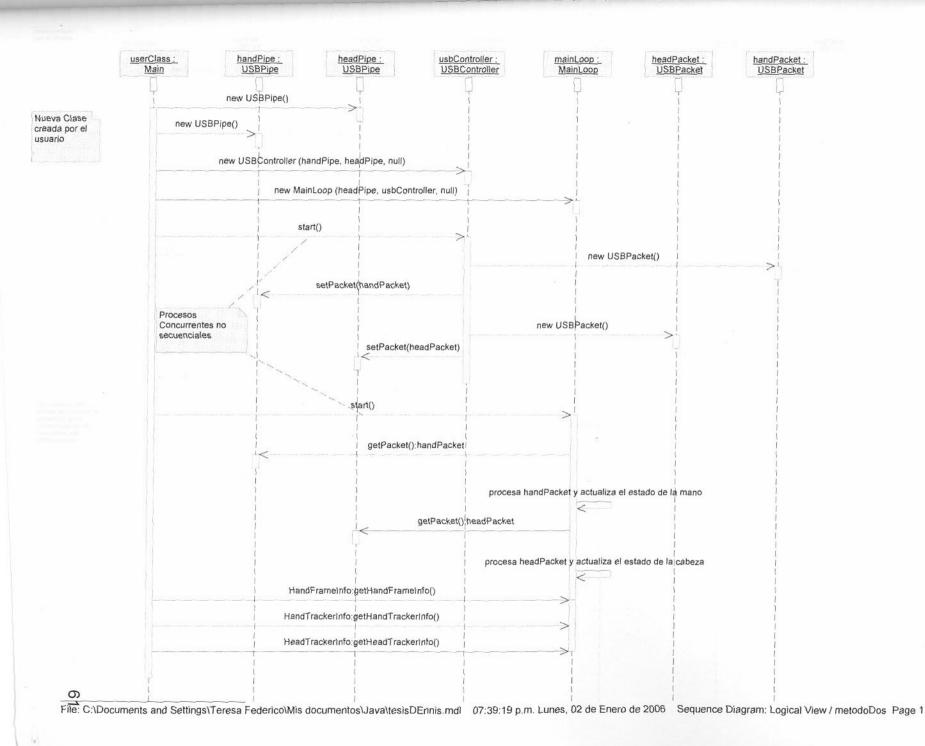

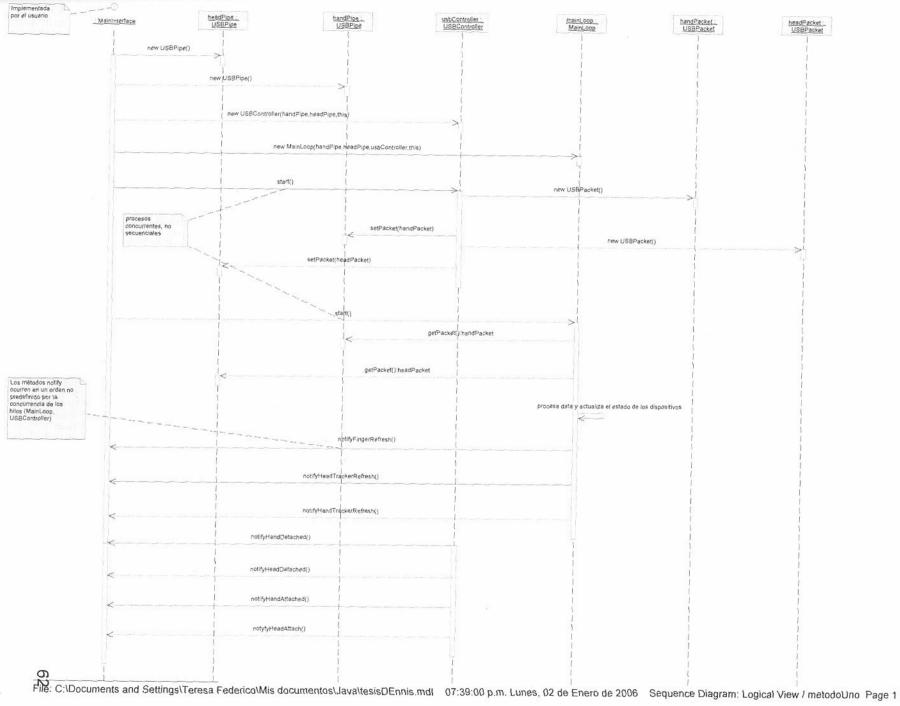

| 15. Diagrama de secuencias, ejemplo de uso #1 del API                       |

| 16. Diagrama de secuencias, ejemplo de uso #2 del API 62                    |

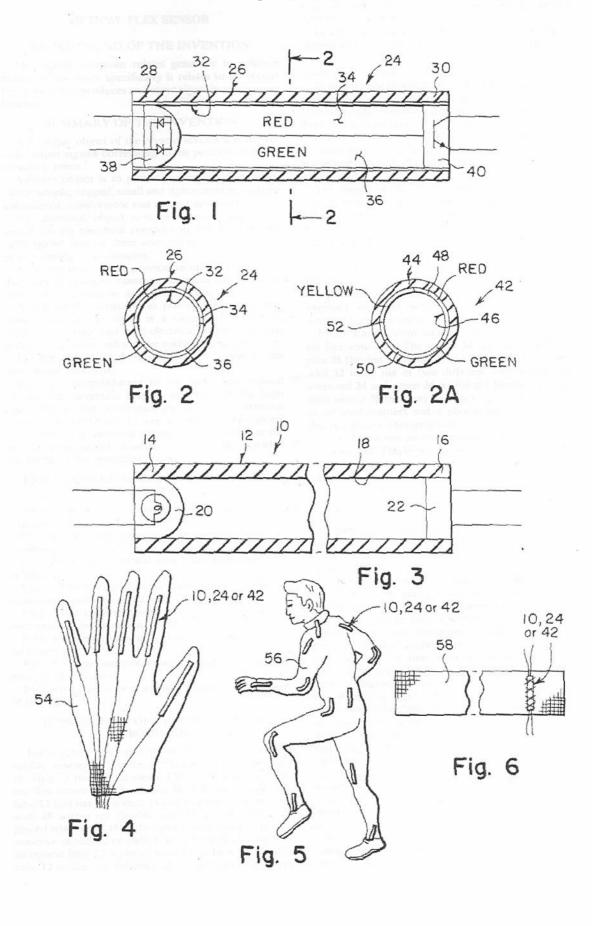

#### 1. Funcionamiento y construcción de los giroscopios de Analog Devices.

# New iMEMS<sup>®</sup> Angular-Rate-Sensing Gyroscope

by John Geen [john.geen@analog.com] and David Krakauer [david.krakauer@analog.com] ADI Micromachined Products Division

#### INTRODUCTION

The new ADXRS150 and ADXRS300 gyros from Analog Devices, with full-scale ranges of 150% and 300%, represent a quantum jump in gyro technology. The first commercially available surface-micromachined angular rate sensors with integrated electronics, they are smaller—with lower power consumption, and better immunity to shock and vibration—than any gyros having comparable functionality. This genuine breakthrough is possible only because of the Analog Devices proprietary integrated micro electro-mechanical system (iMEMS) process, proven by use in millions of automotive accelerometers.

#### **Product Description**

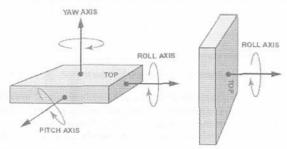

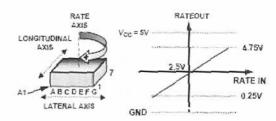

Gyroscopes are used to measure angular rate—how quickly an object turns. The rotation is typically measured in reference to one of three axes: yaw, pitch, or roll.

Figure 1 shows a diagram representing each axis of sensitivity relative to a package mounted to a flat surface. A gyroscope with one axis of sensitivity can also be used to measure other axes by mounting the gyro differently, as shown in the right-hand diagram. Here, a yaw-axis gyro, such as the ADXRS150 or ADXRS300, is mounted on its side so that the yaw axis becomes the roll axis.

Figure 1. Gyro axes of rotational sensitivity. Depending on how a gyro normally sits, its primary axis of sensitivity can be one of the three axes of motion: yaw, pitch, or roll. The ADXRS150 and ADXRS300 are yaw-axis gyros, but they can measure rotation about other axes by appropriate mounting orientation. For example, at the right: a yaw-axis device is positioned to measure roll.

As an example of how a gyro could be used, a yaw-axis gyro mounted on a turntable rotating at 33 1/3 rpm (revolutions per minute) would measure a constant rotation of 360° times 33 1/3 rpm divided by 60 seconds, or 200°/s. The gyro would output a voltage proportional to the angular rate, as determined by its sensitivity, measured in millivolts per degree per second (mV/°/s). The full-scale voltage determines how much angular rate can be measured, so in the example of the turntable, a gyro would

need to have a full-scale voltage corresponding to at least 200°/s. Full-scale is limited by the available voltage swing divided by the sensitivity. The ADXRS300, for example, with 1.5 V full-scale and a sensitivity of 5 mV/°/s, handles a full-scale of 300°/s. The ADXRS150, has a more limited full-scale of 150°/s but a greater sensitivity of 12.5 mV/°/s.

One practical application is to measure how quickly a car turns by mounting a gyro inside the vehicle; if the gyro senses that the car is spinning out of control, differential braking engages to bring it back into control. The angular rate can also be integrated over time to determine angular position—particularly useful for maintaining continuity of GPS-based navigation when the satellite signal is lost for short periods of time.

#### **Coriolis Acceleration**

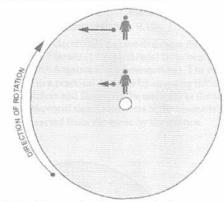

Analog Devices\* ADXRS gyros measure angular rate by means of Coriolis acceleration. The Coriolis effect can be explained as follows, starting with Figure 2. Consider yourself standing on a rotating platform, near the center. Your speed relative to the ground is shown as the blue arrow lengths in Figure 2. If you were to move to a point near the outer edge of the platform, your speed would increase relative to the ground, as indicated by the longer blue arrow. The rate of increase of your tangential speed, caused by your radial velocity, is the *Coriolis* acceleration (after Gaspard G. de Coriolis, 1792-1843—a French mathematician).

If  $\Omega$  is the angular rate and r the radius, the tangential velocity is  $\Omega r$ . So, if r changes at speed, v, there will be a tangential acceleration  $\Omega v$ . This is half of the Coriolis acceleration. There is another half from changing the direction of the radial velocity giving a total of  $2\Omega v$  (see the Appendix). If you have mass, M, the platform must apply a force,  $2M\Omega v$ , to cause that acceleration, and the mass experiences a corresponding reaction force.

Figure 2. Coriolis acceleration example. A person moving northward toward the outer edge of a rotating platform must increase the westward speed component (blue arrows) to maintain a northbound course. The acceleration required is the *Coriolis acceleration*.

The ADXRS gyros take advantage of this effect by using a resonating mass analogous to the person moving out and in on a rotating platform. The mass is micromachined from polysilicon and is tethered to a polysilicon frame so that it can resonate only along one direction.

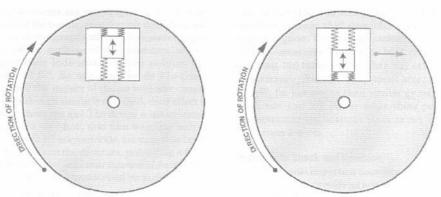

Figure 3. Demonstration of Coriolis effect in response to a resonating silicon mass suspended inside a frame. The orange arrows indicate the force applied to the structure, based on status of the resonating mass.

Figure 3 shows that when the resonating mass moves toward the outer edge of the rotation, it is accelerated to the right and exerts on the frame a reaction force to the left. When it moves toward the center of the rotation, it exerts a force to the right, as indicated by the orange arrows.

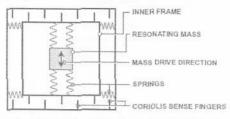

To measure the Coriolis acceleration, the frame containing the resonating mass is tethered to the substrate by springs at 90° relative to the resonating motion, as shown in Figure 4. This figure also shows the Coriolis sense fingers that are used to capacitively sense displacement of the frame in response to the force exerted by the mass, as described further on. If the springs have a stiffness, K, then the displacement resulting from the reaction force will be  $2 \Omega vM/K$ .

Figure 4. Schematic of the gyro's mechanical structure.

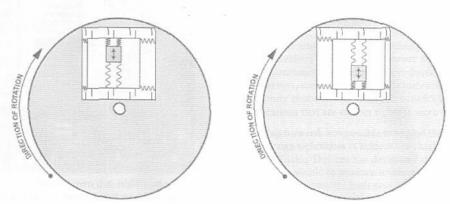

Figure 5, which shows the complete structure, demonstrates that as the resonating mass moves, and as the surface to which the gyro is mounted rotates, the mass and its frame experience the Coriolis acceleration and are translated 90° from the

vibratory movement. As the rate of rotation increases, so does the displacement of the mass and the signal derived from the corresponding capacitance change.

It should be noted that the gyro may be placed anywhere on the rotating object and at any angle, so long as its sensing axis is parallel to the axis of rotation. The above explanation is intended to give an intuitive sense of the function and has been simplified by the placement of the gyro.

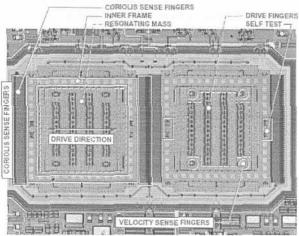

#### **Capacitive Sensing**

ADXRS gyros measure the displacement of the resonating mass and its frame due to the Coriolis effect through capacitive sensing elements attached to the resonator, as shown in Figures 4, 5, and 6. These elements are silicon beams inter-digitated with two sets of stationary silicon beams attached to the substrate, thus forming two nominally equal capacitors. Displacement due to angular rate induces a differential capacitance in this system. If the total capacitance is C and the spacing of the beams is g, then the differential capacitance is  $2 \Omega vMC/gK$ , and is directly proportional to the angular rate. The fidelity of this relationship is excellent in practice, with nonlinearity less than 0.1%.

The ADXRS gyro electronics can resolve capacitance changes as small as  $12\times 10^{-21}$  farads (12 zeptofarads) from beam deflections as small as 0.00016 Angstroms (16 femtometers). The only way this can be utilized in a practical device is by situating the electronics, including amplifiers and filters, on the same die as the mechanical sensor. The differential signal alternates at the resonator frequency and can be extracted from the noise by correlation.

Figure 5. The frame and resonating mass are displaced laterally in response to the Coriolis effect. The displacement is determined from the change in capacitance between the Coriolis sense fingers on the frame and those attached to the substrate.

These sub atomic displacements are meaningful as the average positions of the surfaces of the beams, even though the individual atoms on the surface are moving randomly by much more. There are about 10<sup>12</sup> atoms on the surfaces of the capacitors, so the statistical averaging of their individual motions reduces the uncertainty by a factor of 10<sup>6</sup>. So why can't we do 100 times better? The answer is that the impact of the air molecules causes the structure to move—although similarly averaged, their effect is far greater! So why not remove the air? The device is not operated in a vacuum because it is a very fine, thin film weighing only 4 micrograms; its flexures, only 1.7 microns wide, are suspended over the silicon substrate. Air cushions the structure, preventing it from being destroyed by violent shocks—even those experienced during firing of a guided shell from a howitzer (as demonstrated recently).

Figure 6. Photograph of mechanical sensor. The ADXRS gyros include two structures to enable differential sensing in order to reject environmental shock and vibration.

#### **Features**

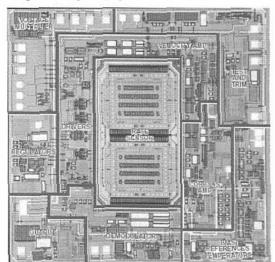

Integration of electronics and mechanical elements is a key feature of products such as the ADXRS150 and ADXRS300, because it makes possible the smallest size and cost for a given performance level. Figure 7 is a photograph of the ADXRS die.

Figure 7. Photograph of ADXRS gyro die, highlighting the integration of the mechanical rate sensor and the signal conditioning electronics.

The ADXRS150 and ADXRS300 are housed in an industry-standard package that simplifies users' product development and production. The ceramic package—a 32-pin ball grid-array, (BGA)—measures 7 mm wide by 7 mm deep by 3 mm tall. It is at least 100 times smaller than any other gyro having similar performance. Besides their small size, these gyros consume 30 mW, far less power than similar gyros. The combination of small size and low power make these products ideally suited for consumer applications such as toy robots, scooters, and navigation devices.

#### Immunity to Shock and Vibration

One of the most important concerns for a gyro user is the device's ability to reliably provide an accurate angular rate-output signal—even in the presence of environmental shock and vibration. One example of such an application is automotive rollover detection, in which a gyro is used to detect whether or not a car (or SUV) is rolling over. Some rollover events are triggered by an impact with another object, such as a curb, that results in a shock to the vehicle. If the shock saturates the gyro sensor, and the gyro cannot filter it out, then the airbags may not deploy. Similarly, if a bump in the road results in a shock or vibration that translates into a rotational signal, the airbags might deploy when not needed—a considerable safety hazard!

As can be seen in Figures 6 and 7, the ADXRS gyros employ a novel approach to angular rate-sensing that makes it possible to reject shocks of up to 1,000g-they use two resonators to differentially sense signals and reject common-mode external accelerations that are unrelated to angular motion. This approach is, in part, the reason for the excellent immunity of the ADXRS gyros to shock and vibration. The two resonators in Figure 6 are mechanically independent, and they operate anti-phase. As a result, they measure the same magnitude of rotation, but give outputs in opposite directions. Therefore, the difference between the two sensor signals is used to measure angular rate. This cancels non-rotational signals that affect both sensors. The signals are combined in the internal hard-wiring ahead of the very sensitive preamplifiers. Thus, extreme acceleration overloads are largely prevented from reaching the electronicsthereby allowing the signal conditioning to preserve the angular rate output during large shocks. This scheme requires that the two sensors be well-matched, precisely fabricated copies of each other.

#### SUMMARY

Analog Devices has used its iMEMS process to achieve a breakthrough with the development of the World's first fully integrated angular rate sensor. Integration yields a revolution in reliability, size, and price. The result is a gyro that is suited for a much wider range of applications than previously thought possible or affordable. The device's low power and small size will benefit small consumer and industrial products that run on batteries, such as toys, scooters, and portable instruments. The tremendous immunity to shock and vibration benefits automotive and other applications that are subject to harsh environmental conditions.

Looking forward, it is possible to exploit the iMEMS process and gyro design techniques to achieve even higher levels of integration. Just as Analog Devices has developed dual-axis accelerometers, it will be possible to produce multi-axis gyroscopes. It will even be possible to integrate both accelerometers and gyros on a single die. The resulting inertial measurement unit would enable even tiny vehicles to be stabilized and navigated autonomously.

# MICROCHIP PIC18F2455/2550/4455/4550

# 28/40/44-Pin High-Performance, Enhanced Flash USB Microcontrollers with nanoWatt Technology

#### Universal Serial Bus Features:

- · USB V2.0 Compliant

- . Low Speed (1.5 Mb/s) and Full Speed (12 Mb/s)

- Supports Control, Interrupt, Isochronous and Bulk Transfers

- Supports up to 32 endpoints (16 bidirectional)

- · 1-Kbyte dual access RAM for USB

- On-chip USB transceiver with on-chip voltage regulator

- · Interface for off-chip USB transceiver

- Streaming Parallel Port (SPP) for USB streaming transfers (40/44-pin devices only)

#### Power-Managed Modes:

- · Run: CPU on, peripherals on

- · Idle: CPU off, peripherals on

- . Sleep: CPU off, peripherals off

- Idle mode currents down to 5.8 μA typical.

- . Sleep mode currents down to 0.1 µA typical

- Timer1 oscillator: 1.1 μA typical, 32 kHz, 2V

- · Watchdog Timer: 2.1 µA typical

- · Two-Speed Oscillator Start-up

#### Flexible Oscillator Structure:

- Four Crystal modes including High Precision PLL for USB

- . Two External Clock modes, up to 48 MHz

- · Internal oscillator block:

- 8 user-selectable frequencies, from 31 kHz to 8 MHz

- User-tunable to compensate for frequency drift

- Secondary oscillator using Timer1 @ 32 kHz

- Dual oscillator options allow microcontroller and USB module to run at different clock speeds

- · Fail-Safe Clock Monitor

- Allows for safe shutdown if any clock stops

#### Peripheral Highlights:

- · High-current sink/source 25 mA/25 mA

- · Three external interrupts

- · Four Timer modules (Timer0 to Timer3)

- . Up to 2 Capture/Compare/PWM (CCP) modules:

- Capture is 16-bit, max. resolution 6.25 ns (TcY/16)

- Compare is 16-bit, max. resolution 100 ns (TCY)

- PWM output: PWM resolution is 1 to 10-bit

- Enhanced Capture/Compare/PWM (ECCP) module:

- Multiple output modes

- Selectable polarity

- Programmable dead time

- Auto-Shutdown and Auto-Restart

- · Enhanced USART module:

- LIN bus support

- Master Synchronous Serial Port (MSSP) module supporting 3-wire SPI™ (all 4 modes) and I<sup>2</sup>C™ Master and Slave modes

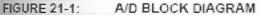

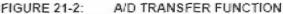

- 10-bit, up to 13-channels Analog-to-Digital Converter module (A/D) with programmable acquisition time

- Dual analog comparators with input multiplexing

#### Special Microcontroller Features:

- C compiler optimized architecture with optional extended instruction set

- 100,000 erase/write cycle Enhanced Flash program memory typical

- 1,000,000 erase/write cycle Data EEPROM memory typical

- Flash/Data EEPROM Retention: > 40 years

- Self-programmable under software control

- · Priority levels for interrupts

- · 8 x 8 Single-Cycle Hardware Multiplier

- · Extended Watchdog Timer (WDT);

- Programmable period from 41 ms to 131s

- Programmable Code Protection

- Single-Supply 5V In-Circuit Serial Programming™ (ICSP™) via two pins

- · In-Circuit Debug (ICD) via two pins

- Optional dedicated ICD/ICSP port (44-pin devices only)

- Wide operating voltage range (2.0V to 5.5V)

|            | Prog             | ram Memory                    | Data            | Memory            |     | 3 410              | 4 4 1             | MSSP |      | RT tors                     |         |          |                    |

|------------|------------------|-------------------------------|-----------------|-------------------|-----|--------------------|-------------------|------|------|-----------------------------|---------|----------|--------------------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | 10-bit<br>A/D (ch) | CCP/ECCP<br>(PWM) | SPP  | SPI™ | Master<br>I <sup>2</sup> C™ | EAUSART | Comparat | Timers<br>8/16-bit |

| PIC18F2455 | 24K              | 12288                         | 2048            | 258               | 24  | 10                 | 2/0               | No   | Y    | Y                           | 1       | 2        | 1/3                |

| PIC18F2550 | 32K              | 16384                         | 2048            | 256               | 24  | 10                 | 2/0               | No   | Y    | Y                           | 1       | 2        | 1/3                |

| PIC18F4455 | 24K              | 12288                         | 2048            | 256               | 35  | 13                 | 1/1               | Yes  | Y    | Y                           | 1       | 2        | 1/3                |

| PIC18F4550 | 32K              | 16384                         | 2048            | 256               | 35  | 13                 | 1/1               | Yes  | Y    | Y                           | 1       | 2        | 1/3                |

#### 3. Módulo USB del Microcontrolador PIC 18f4550.

# 17.0 UNIVERSAL SERIAL BUS (USB)

This section describes the details of the USB peripheral. Because of the very specific nature of the module, knowledge of USB is expected. Some high-level USB information is provided in Section 17.10 "Overview of USB" only for application design reference. Designers are encouraged to refer to the official specification published by the USB Implementers Forum (USB-IF) for the latest information. USB Specification Revision 2.0 is the most current specification at the time of publication of this document.

#### 17.1 Overview of the USB Peripheral

The PIC18FX455/X550 device family contains a full speed and low-speed compatible USB Serial Interface Engine (SIE) that allows fast communications between any USB host and the PIC® microcontroller. The SIE

can be interfaced directly to the USB, utilizing the internal transceiver, or it can be connected through an external transceiver. An internal 3.3V regulator is also available to power the internal transceiver in 5V applications.

Some special hardware features have been included to improve performance. Dual port memory in the device's data memory space (USB RAM) has been supplied to share direct memory access between the microcontroller core and the SIE. Buffer descriptors are also provided, allowing users to freely program endpoint memory usage within the USB RAM space. A Streaming Parallel Port has been provided to support the uninterrupted transfer of large volumes of data, such as isochronous data, to external memory buffers.

Figure 17-1 presents a general overview of the USB peripheral and its features.

FIGURE 17-1: **USB PERIPHERAL AND OPTIONS** PIC18FX455/X550 Family 3.3V Regulator External 3.3V Supply<sup>(3)</sup> -⊠ Vuse EN VREGEN Optional External Pull-ups<sup>(2)</sup> FSEN UPUEN Internal Pull-ups (Full (Low Speed) UTRDIS -Speed) I Transceiver USB Bus USB Clock from the FS Oscillator Module QΕ External → □ ○E(1) ■◆ Ø VM(¹) Transceiver USB Control USB Bus and 4-⊠ ∨P(1) Configuration RCV(1) USB ↓→⊠ ∨мо<sup>(1)</sup> SIE →Ø VPO(1) ►> SPP7:SPP0 →⊠ CK1SPP 1 Kbyte USB RAM ►X CK2SPP →⊠ CSSPP →X OESPP Note 1: This signal is only available if the internal transceiver is disabled (UTRDIS = 1). 2: The internal pull-up resistors should be disabled (UPUEN = 0) if external pull-up resistors are used. 3: Do not enable the internal regulator when using an external 3.3V supply.

The PPBRST bit (UCON<6>) controls the Reset status when Double-Buffering mode (ping-pong buffering) is used. When the PPBRST bit is set, all ping-pong buffer pointers are set to the Even buffers. PPBRST has to be cleared by firmware. This bit is ignored in buffering modes not using ping-pong buffering.

The PKTDIS bit (UCON<4>) is a flag indicating that the SIE has disabled packet transmission and reception. This bit is set by the SIE when a SETUP token is received to allow setup processing. This bit cannot be set by the microcontroller, only cleared; clearing it allows the SIE to continue transmission and/or reception. Any pending events within the Buffer Descriptor Table will still be available, indicated within the USTAT register's FIFO buffer.

The RESUME bit (UCON<2>) allows the peripheral to perform a remote wake-up by executing Resume signaling. To generate a valid remote wake-up, firmware must set RESUME for 10 ms and then clear the bit. For more information on Resume signaling, see Sections 7.1.7.5, 11.9 and 11.4.4 in the USB 2.0 specification.

The SUSPND bit (UCON<1>) places the module and supporting circuitry (i.e., voltage regulator) in a low-power mode. The input clock to the SIE is also disabled. This bit should be set by the software in response to an IDLEIF interrupt. It should be reset by the microcontroller firmware after an ACTVIF interrupt is observed. When this bit is active, the device remains attached to the bus but the transceiver outputs remain Idle. The voltage on the VUSB pin may vary depending on the value of this bit. Setting this bit before a IDLEIF request will result in unpredictable bus behavior.

Note: While in Suspend mode, a typical bus powered USB device is limited to 500 μA of current. This is the complete current drawn by the PICmicro device and its supporting circuitry. Care should be taken to assure minimum current draw when the device enters Suspend mode.

# 17.2.2 USB CONFIGURATION REGISTER (UCFG)

Prior to communicating over USB, the module's associated internal and/or external hardware must be configured. Most of the configuration is performed with the UCFG register (Register 17-2). The separate USB voltage regulator (see Section 17.2.2.8 "Internal Regulator") is controlled through the configuration registers.

The UFCG register contains most of the bits that control the system level behavior of the USB module. These include:

- Bus speed (full speed versus low speed)

- · On-chip pull-up resistor enable

- · On-chip transceiver enable

- · Ping-pong buffer usage

The UCFG register also contains two bits which aid in module testing, debugging and USB certifications. These bits control output enable state monitoring and eye pattern generation.

Note: The USB speed, transceiver and pull-up should only be configured during the module setup phase. It is not recommended to switch these settings while the module is enabled.

#### 17.2.2.1 Internal Transceiver

The USB peripheral has a built-in USB 2.0 full speed and low-speed compliant transceiver, internally connected to the SIE. This feature is useful for low-cost single chip applications. The UTRDIS bit (UCFG<3>) controls the transceiver; it is enabled by default (UTRDIS = 0). The FSEN bit (UCFG<2>) controls the transceiver speed; setting the bit enables full speed operation.

The on-chip USB pull-up resistors are controlled by the UPUEN bit (UCFG<4>). They can only be selected when the on-chip transceiver is enabled.

The USB specification requires 3.3V operation for communications; however, the rest of the chip may be running at a higher voltage. Thus, the transceiver is supplied power from a separate source, VUSB.

#### 17.2.2.2 External Transceiver

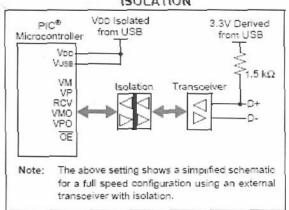

This module provides support for use with an off-chip transceiver. The off-chip transceiver is intended for applications where physical conditions dictate the location of the transceiver to be away from the SIE. For example, applications that require isolation from the USB could use an external transceiver through some isolation to the microcontroller's SIE (Figure 17-2). External transceiver operation is enabled by setting the UTRDIS bit.

# FIGURE 17-2: TYPICAL EXTERNAL TRANSCEIVER WITH ISOLATION

#### REGISTER 17-2: UCFG: USB CONFIGURATION REGISTER

|         | R/W-0    | R/W-0                                                          | U-0        | R/W-0                      | R/W-0         | R/W-0        | R/W-0      | R/W-0  |

|---------|----------|----------------------------------------------------------------|------------|----------------------------|---------------|--------------|------------|--------|

|         | UTEYE    | UOEMON(1)                                                      |            | UPUEN(2,3)                 | UTRDIS(2)     | FSEN(2)      | PPB1       | PPB0   |

|         | bit 7    | inded Zela                                                     |            | Buttering                  |               |              | Gr. Tone   | bit 0  |

| bit 7   | UTEYE:   | JSB Eye Pattern                                                | Test En    | nable bit                  |               |              |            |        |

|         |          | pattern test enak<br>pattern test disal                        |            |                            |               |              |            |        |

| bit 6   | UOEMON   | N: USB OE Moni                                                 | itor Enab  | ple bit(1)                 |               |              |            |        |

|         |          | ignal active; it in<br>signal inactive                         | dicates i  | intervals during           | which the D   | +/D- lines a | re driving |        |

| bit 5   | Unimple  | mented: Read a                                                 | is '0'     |                            |               |              |            |        |

| bit 4   | UPUEN:   | USB On-Chip Pi                                                 | ull-up En  | able bit <sup>(2,3</sup> ) |               |              |            |        |

|         |          | hip pull-up enabi<br>nip pull-up disab                         |            | up on D+ with F            | SEN ≈ 1 or    | D- with FS   | EN = 0)    |        |

| bit 3   | UTRDIS:  | On-Chip Transc                                                 | eiver Dis  | sable bit <sup>(2)</sup>   |               |              |            |        |

|         |          | hip transceiver d<br>nip transceiver a                         |            | digital transcei           | ver interface | enabled      |            |        |

| bit 2   | FSEN: Fu | ull Speed Enable                                               | bit(2)     |                            |               |              |            |        |

|         |          | peed device; co<br>speed device; co                            |            | -                          |               |              |            |        |

| bit 1-0 | PPB1:PP  | B0: Ping-Pong                                                  | Buffers (  | Configuration bi           | ts            |              |            |        |

|         | 01 = Eve | erved<br>n/Odd ping-pong<br>n/Odd ping-pong<br>n/Odd ping-pong | buffer e   | enabled for OU             |               |              |            |        |

|         | Note 1   | : If UTRDIS is                                                 | set, the 🤇 | DE signal will b           | e active inde | pendent of   | the UOEM   | ON bit |

- - 2: The UPUEN, UTRDIS and FSEN bits should never be changed while the USB module is enabled. These values must be preconfigured prior to enabling the

- 3: This bit is only valid when the on-chip transceiver is active (UTRDIS = 0); otherwise, it is ignored.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

There are 6 signals from the module to communicate with and control an external transceiver:

- VM: Input from the single-ended D-line

- VP: Input from the single-ended D+ line

- · RCV: Input from the differential receiver

- · VMO: Output to the differential line driver

- · VPO: Output to the differential line driver

- OE: Output enable

The VPO and VMO signals are outputs from the SIE to the external transceiver. The RCV signal is the output from the external transceiver to the SIE; it represents the differential signals from the serial bus translated into a single pulse train. The VM and VP signals are used to report conditions on the serial bus to the SIE that can't be captured with the RCV signal. The combinations of states of these signals and their interpretation are listed in Table 17-1 and Table 17-2.

TABLE 17-1: DIFFERENTIAL OUTPUTS TO TRANSCEIVER

| VPO | VMO | Bus State         |    |

|-----|-----|-------------------|----|

| 0   | 0   | Single-Ended Zero |    |

| 0   | 1   | Differential '0'  |    |

| 1   | 0   | Differential '1'  |    |

| 1   | 1   | Illegal Condition | 40 |

TABLE 17-2: SINGLE-ENDED INPUTS FROM TRANSCEIVER

| VP VM |     | Bus State         |  |  |  |  |  |

|-------|-----|-------------------|--|--|--|--|--|

| 0     | 0   | Single-Ended Zero |  |  |  |  |  |

| 0     | 1 2 | Low Speed         |  |  |  |  |  |

| 1     | 0   | High Speed        |  |  |  |  |  |

| 1     | 1   | Error             |  |  |  |  |  |

The  $\overline{OE}$  signal toggles the state of the external transceiver. This line is pulled low by the device to enable the transmission of data from the SIE to an external device.

#### 17.2.2.3 Internal Pull-up Resistors

The PIC18FX455/X550 devices have built-in pull-up resistors designed to meet the requirements for low-speed and full speed USB. The UPUEN bit (UCFG<4>) enables the internal pull-ups. Figure 17-1 shows the pull-ups and their control.

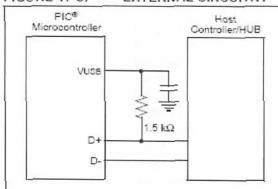

#### 17.2.2.4 External Pull-up Resistors

External pull-up may also be used. The VUSB pin may be used to pull up D+ or D-. The pull-up resistor must be 1.5 k $\Omega$  (±5%) as required by the USB specifications. Figure 17-3 shows an example.

FIGURE 17-3: EXTERNAL CIRCUITRY

Note: The above setting shows a typical connection for a full speed configuration using an on-chip regulator and an external pull-up resistor.

#### 17.2.2.5 Ping-Pong Buffer Configuration

The usage of ping-pong buffers is configured using the PPB1:PPB0 bits. Refer to Section 17.4.4 "Ping-Pong Buffering" for a complete explanation of the ping-pong buffers.

#### 17.2.2.6 USB Output Enable Monitor

The USB OE monitor provides indication as to whether the SIE is listening to the bus or actively driving the bus. This is enabled by default when using an external transceiver or when UCFG<6> = 1.

The OE monitoring is useful for initial system debugging, as well as scope triggering during eye pattern generation tests.

#### 17.2.2.7 Eye Pattern Test Enable

An automatic eye pattern test can be generated by the module when the UCFG<7> bit is set. The eye pattern output will be observable based on module settings, meaning that the user is first responsible for configuring the SIE clock settings, pull-up resistor and Transceiver mode. In addition, the module has to be enabled.

Once UTEYE is set, the module emulates a switch from a receive to transmit state and will start transmitting a J-K-J-K bit sequence (K-J-K-J for full speed). The sequence will be repeated indefinitely while the Eye Pattern Test mode is enabled.

Note that this bit should never be set while the module is connected to an actual USB system. This test mode is intended for board verification to aid with USB certification tests. It is intended to show a system developer the noise integrity of the USB signals which can be affected by board traces, impedance mismatches and proximity to other system components. It does not properly test the transition from a receive to a transmit state. Although the eye pattern is not meant to replace the more complex USB certification test, it should aid during first order system debugging.

#### 17.2.2.8 Internal Regulator

The PIC 18FX455/X550 devices have a built-in 3.3V regulator to provide power to the internal transceiver and provide a source for the internal/external pull-ups. An external 220 nF (±20%) capacitor is required for stability.

Note: The drive from VUSB is sufficient to only drive an external pull-up in addition to the internal transceiver.

The regulator is enabled by default and can be disabled through the VREGEN configuration bit. When enabled, the voltage is visible on pin VUSE. When the regulator is disabled, a 3.3V source must be provided through the VUSB pin for the internal transceiver. If the internal transceiver is disabled VUSB is not used.

- Note 1: Do not enable the internal regulator if an external regulator is connected to VUSB.

- VDD must be greater than VUSB at all times, even with the regulator disabled.

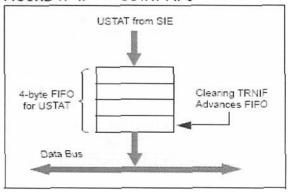

#### 17.2.3 USB STATUS REGISTER (USTAT)

The USB Status register reports the transaction status within the SIE. When the SIE issues a USB transfer complete interrupt, USTAT should be read to determine the status of the transfer. USTAT contains the transfer endpoint number, direction and ping-pong buffer pointer value (if used).

Note: The data in the USB Status register is valid only when the TRNIF interrupt flag is asserted.

The USTAT register is actually a read window into a four-byte status FIFO, maintained by the SIE. It allows the microcontroller to process one transfer while the SIE processes additional endpoints (Figure 17-4). When the SIE completes using a buffer for reading or writing data, it updates the USTAT register. If another USB transfer is performed before a transaction complete interrupt is serviced, the SIE will store the status of the next transfer into the status FIFO.

Clearing the transfer complete flag bit, TRNIF, causes the SIE to advance the FIFO. If the next data in the FIFO holding register is valid, the SIE will immediately reassert the interrupt. If no additional data is present, TRNIF will remain clear; USTAT data will no longer be reliable.

Note: If an endpoint request is received while the USTAT FIFO is full, the SIE will automatically issue a NAK back to the host.

FIGURE 17-4: USTAT FIFO

#### REGISTER 17-3: USTAT: USB STATUS REGISTER

| U-0   | R-x   | R-x   | R-x   | R-x   | R-x | R-x                 | U-0   |

|-------|-------|-------|-------|-------|-----|---------------------|-------|

|       | ENDP3 | ENDP2 | ENDP1 | ENDP0 | DIR | PPBI <sup>(1)</sup> |       |

| bit 7 |       |       |       |       |     |                     | bit ( |

bit 7 Unimplemented: Read as '0'

bit 6-3 ENDP3:ENDP0: Encoded number of last endpoint activity (represents the number of the BDT updated by the last USB transfer)

1111 = Endpoint 15

1110 = Endpoint 14

0001 = Endpoint 1 0000 = Endpoint 0

bit 2 DIR: Last BD Direction Indicator bit

1 = The last transaction was an IN token

0 = The last transaction was an OUT or SETUP token

bit 1 PPBI: Ping-Pong BD Pointer Indicator bit (1)

1 = The last transaction was to the Odd BD bank

0 = The last transaction was to the Even BD bank

Note 1: This bit is only valid for endpoints with available Even and Odd BD registers.

bit 0 Unimplemented: Read as '0'

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 17.2.4 USB ENDPOINT CONTROL

Each of the 16 possible bidirectional endpoints has its own independent control register, UEPn (where 'n' represents the endpoint number). Each register has an identical complement of control bits. The prototype is shown in Register 17-4.

The EPHSHK bit (UEPn<4>) controls handshaking for the endpoint; setting this bit enables USB handshaking. Typically, this bit is always set except when using isochronous endpoints.

The EPCONDIS bit (UEPn<3>) is used to enable or disable USB control operations (SETUP) through the endpoint. Clearing this bit enables SETUP transactions; note that the corresponding EPINEN and EPOUTEN bit must be set to enable IN and OUT

transactions. For Endpoint 0, this bit should always be cleared since the USB specifications identify Endpoint 0 as the default control endpoint.

The EPOUTEN bit (UEPn<2>) is used to enable or disable USB OUT transactions from the host. Setting this bit enables OUT transactions. Similarly, the EPINEN bit (UEPn<1>) enables or disables USB IN transactions from the host.

The EPSTALL bit (UEPn<0>) is used to indicate a STALL condition for the endpoint. If a STALL is issued on a particular endpoint, the EPSTALL bit for that endpoint pair will be set by the SIE. This bit remains set until it is cleared through firmware, or until the SIE is reset.

#### REGISTER 17-4: UEPn: USB ENDPOINT n CONTROL REGISTER (UEP0 THROUGH UEP15)

| U-0   | U-0       | U-0 | R/W-0  | R/W-0    | R/W-0   | R/W-C  | R/W-0      |

|-------|-----------|-----|--------|----------|---------|--------|------------|

|       | 10 pm     | 157 | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL(1) |

| bit 7 | Setan -en |     |        | -        |         |        | 0 tid      |

| bit  | 7-5 | Unimp       | lemented: | Read     | as '0' |

|------|-----|-------------|-----------|----------|--------|

| 2016 | 1   | O 111111132 |           | S COLUMN | 40 0   |

bit 4 EPHSHK: Endpoint Handshake Enable bit

1 = Endpoint handshake enabled

0 = Endpoint handshake disabled (typically used for isochronous endpoints)

bit 3 EPCONDIS: Bidirectional Endpoint Control bit

If EPOUTEN = 1 and EPINEN = 1:

1 = Disable Endpoint n from control transfers; only IN and OUT transfers allowed

0 = Enable Endpoint n for control (SETUP) transfers; IN and OUT transfers also allowed

bit 2 EPOUTEN: Endpoint Output Enable bit

1 = Endpoint n output enabled

0 = Endpoint n output disabled

bit 1 EPINEN: Endpoint Input Enable bit

1 = Endpoint n input enabled

0 = Endpoint n input disabled

bit 0 EPSTALL: Endpoint Stall Enable bit(1)

1 = Endpoint n is stalled

0 = Endpoint n is not stalled

Note 1: Valid only if Endpoint n is enabled; otherwise, the bit is ignored.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | f bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 17.2.5 USB ADDRESS REGISTER (UADDR)

The USB Address register contains the unique USB address that the peripheral will decode when active. UADDR is reset to 00h when a USB Reset is received, indicated by URSTIF, or when a Reset is received from the microcontroller. The USB address must be written by the microcontroller during the USB setup phase (enumeration) as part of the Microchip USB firmware support.

## 17.2.6 USB FRAME NUMBER REGISTERS (UFRMH:UFRML)

The Frame Number registers contain the 11-bit frame number. The low-order byte is contained in UFRML, while the three high-order bits are contained in UFRMH. The register pair is updated with the current frame number whenever a SOF token is received. For the microcontroller, these registers are read-only. The Frame Number register is primarily used for isochronous transfers.

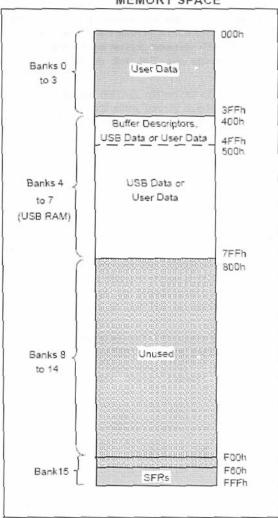

#### 17.3 USB RAM

USB data moves between the microcontroller core and the SIE through a memory space known as the USB RAM. This is a special dual port memory, that is mapped into the normal data memory space in Banks 4 through 7 (400h to 7FFh), for a total of 1 Kbyte (Figure 17-5).

Bank 4 (400h through 4FFh) is used specifically for endpoint buffer control, while Banks 5 through 7 are available for USB data. Depending on the type of buffering being used, all but 8 bytes of Bank 4 may also be available for use as USB buffer space.

Although USB RAM is available to the microcontroller as data memory, the sections that are being accessed by the SIE should not be accessed by the microcontroller. A semaphore mechanism is used to determine the access to a particular buffer at any given time. This is discussed in Section 17.4.1.1 "Buffer Ownership".

FIGURE 17-5: IMPLEMENTATION OF USB RAM IN DATA MEMORY SPACE

The BDnSTAT byte of the BDT should always be the last byte updated when preparing to arm an endpoint. The SIE will clear the UOWN bit when a transaction has completed. The only exception to this is when KEN is enabled and/or BSTALL is enabled.

No hardware mechanism exists to block access when the UOWN bit is set. Thus, unexpected behavior can occur if the microcontroller attempts to modify memory when the SIE owns it. Similarly, reading such memory may produce inaccurate data until the USB peripheral returns ownership to the microcontroller.

#### 17.4.1.2 BDnSTAT Register (CPU Mode)

When UOWN = 0, the microcontroller core owns the BD. At this point, the other seven bits of the register take on control functions.

The Keep Enable bit, KEN (BDnSTAT<5>), determines if a BD stays enabled. If the bit is set, once the UOWN bit is set, it will remain owned by the SIE independent of the endpoint activity. This prevents the USTAT FIFO from being updated, as well as the transaction complete interrupt from being set for the endpoint. This feature should only be enabled when the Streaming Parallel Port is selected as the data I/O channel instead of USB RAM.

The Address Increment Disable bit, INCDIS (BDnSTAT<4>), controls the SIE's automatic address increment function. Setting INCDIS disables the auto-increment of the buffer address by the SIE for each byte transmitted or received. This feature should only be enabled when using the Streaming Parallel Port, where each data byte is processed to or from the same memory location.

The Data Toggle Sync Enable bit, DTSEN (BDnSTAT<3>), controls data toggle parity checking. Setting DTSEN enables data toggle synchronization by

the SIE; when enabled, it checks the data packet's parity against the value of DTS (BDnSTAT<6>). If a packet arrives with an incorrect synchronization, the data will essentially be ignored; it will not be written to the USB RAM and the USB transfer complete interrupt flag will not be set. The SIE will send an ACK token back to the host to Acknowledge receipt, however. The effects of the DTSEN bit on the SIE are summarized in Table 17-3.

The Buffer Stall bit, BSTALL (BDnSTAT<2>), provides support for control transfers, usually one-time stalls on Endpoint 0. It also provides support for the SET\_FEATURE/CLEAR\_FEATURE commands specified in Chapter 9 of the USB specification; typically, continuous STALLs to any endpoint other than the default control endpoint.

The BSTALL bit enables buffer stalls. Setting BSTALL causes the SIE to return a STALL token to the host if a received token would use the BD in that location. The EPSTALL bit in the corresponding UEPn control register is set and a STALL interrupt is generated when a STALL is issued to the host. The UOWN bit remains set and the BDs are not changed unless a SETUP token is received. In this case, the STALL condition is cleared and the ownership of the BD is returned to the microcontroller core.

The BD9:BD8 bits (BDnSTAT<1:0>) store the two most significant digits of the SIE byte count; the lower 8 digits are stored in the corresponding BDnCNT register. See Section 17.4.2 "BD Byte Count" for more information.

TABLE 17-3: EFFECT OF DTSEN BIT ON ODD/EVEN (DATA0/DATA1) PACKET RECEPTION

| OUT Packet         | BDnSTAT | Settings | Device Response after Receiving Packet |      |       |                          |  |  |

|--------------------|---------|----------|----------------------------------------|------|-------|--------------------------|--|--|

| from Host          | DTSEN   | DTS      | Handshake                              | UOWN | TRNIF | BDnSTAT and USTAT Status |  |  |

| DATA0              | 1       | 0        | ACK                                    | 0    | 1     | Updated                  |  |  |

| DATA1              | 1       | 0        | ACK                                    | 1    | 0     | Not Updated              |  |  |

| DATAO              | 1       | 1        | ACK                                    | 0    | 1     | Updated                  |  |  |

| DATA1              | 1       | 1        | ACK                                    | 1    | 0     | Not Updated              |  |  |

| Either             | 0       | x        | ACK                                    | 0    | 1     | Updated                  |  |  |

| Either, with error | ×       | х        | NAK                                    | 1    | 0     | Not Updated              |  |  |

Legend: x = don't care

#### REGISTER 17-5: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER (BD0STAT THROUGH BD63STAT), CPU MODE (DATA IS WRITTEN TO THE SIDE)

| RW-x    | R/W-x              | R/W-x | R/W-x  | RM-x  | R/W-x  | R/W-x | R/W-x |

|---------|--------------------|-------|--------|-------|--------|-------|-------|

| UOWN(1) | DTS <sup>(2)</sup> | KEN   | INCDIS | DTSEN | BSTALL | BC9   | вс8   |

| bit 7   |                    |       |        |       |        |       | hit ( |

UOWN: USB Own bit(1) bit 7

0 = The microcontroller core owns the BD and its corresponding buffer

DTS: Data Toggle Synchronization bit (2) bit 6

1 = Data 1 packet

0 = Data 0 packet

bit 5 KEN: BD Keep Enable bit

> 1 = USB will keep the BD indefinitely once UOWN is set (required for SPP endpoint configuration)

0 = USB will hand back the BD once a token has been processed

bit 4 INCDIS: Address Increment Disable bit

1 = Address increment disabled (required for SPP endpoint configuration)

0 = Address increment enabled

bit 3 DTSEN: Data Toggle Synchronization Enable bit

> 1 = Data toggle synchronization is enabled; data packets with incorrect Sync value will be ignored

0 = No data toggle synchronization is performed

bit 2 BSTALL: Buffer Stall Enable bit

> 1 = Buffer stall enabled; STALL handshake issued if a token is received that would use the BD. in the given location (UOWN bit remains set, BD value is unchanged)

0 = Buffer stall disabled

bit 1-0 BC9:BC8: Byte Count bits 9 and 8

> The byte count bits represent the number of bytes that will be transmitted for an IN token or received during an OUT token. Together with BC<7:0>, the valid byte counts are 0-1023.

Note 1: This bit must be initialized by the user to the desired value prior to enabling the USB module.

2: This bit is ignored unless DTSEN = 1.

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 17.4.1.3 BDnSTAT Register (SIE Mode)

When the BD and its buffer are owned by the SIE, most of the bits in BDnSTAT take on a different meaning. The configuration is shown in Register 17-6. Once UOWN is set, any data or control settings previously written there by the user will be overwritten with data from the SIE.

The BDnSTAT register is updated by the SIE with the token Packet Identifier (PID), which is stored in BDnSTAT<5:3>. The transfer count in the corresponding BDnCNT register is updated; values that overflow the 8-bit register carry over to the two most significant digits of the count, stored in BDnSTAT<1:0>.

#### 17.4.2 BD BYTE COUNT

The byte count represents the total number of bytes that will be transmitted during an IN transfer. After an IN transfer, the SIE will return the number of bytes sent to the host.

For an OUT transfer, the byte count represents the maximum number of bytes that can be received and stored in USB RAM. After an OUT transfer, the SIE will return the actual number of bytes received. If the number of bytes received exceeds the corresponding byte count, the data packet will be rejected and a NAK handshake will be generated. When this happens, the byte count will not be updated.

The 10-bit byte count is distributed over two registers. The lower 8 bits of the count reside in the BDnCNT register. The upper two bits reside in BDnSTAT<1:0>. This represents a valid byte range of 0 to 1023.

#### 17.4.3 BD ADDRESS VALIDATION

The BD Address register pair contain the starting RAM address location for the corresponding endpoint buffer. For an endpoint starting location to be valid, it must fall in the range of the USB RAM, 400h to 7FFh. No mechanism is available in hardware to validate the BD address.

If the value of the BD address does not point to an address in the USB RAM, or if it points to an address within another endpoint's buffer, data is likely to be lost or overwritten. Similarly, overlapping a receive buffer (OUT endpoint) with a BD location in use can yield unexpected results. When developing USB applications, the user may want to consider the inclusion of software-based address validation in their code.

# REGISTER 17-6: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER (BD0STAT THROUGH BD63STAT), SIE MODE (DATA RETURNED BY THE SIDE TO THE MICROCONTROLLER)

|                                | R/W-x |

|--------------------------------|-------|

| UOWN - PID3 PID2 PID1 PID0 BC9 | BC8   |

bit 7 UOWN: USB Own bit

1 = The SIE owns the BD and its corresponding buffer

bit 6 Reserved: Not written by the SIE

bit 5-2 PID3:PID0: Packet Identifier bits

The received token PID value of the last transfer (IN, OUT or SETUP transactions only).

bit 1-0 BC9:BC8: Byte Count bits 9 and 8

These bits are updated by the SIE to reflect the actual number of bytes received on an OUT transfer and the actual number of bytes transmitted on an IN transfer.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

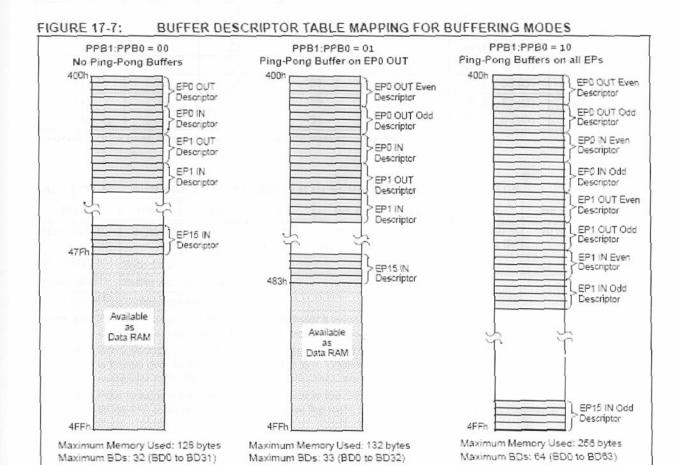

#### 17.4.4 PING-PONG BUFFERING

An endpoint is defined to have a ping-pong buffer when it has two sets of BD entries: one set for an Even transfer and one set for an Odd transfer. This allows the CPU to process one BD while the SIE is processing the other BD. Double-buffering BDs in this way allows for maximum throughput to/from the USB.

The USB module supports three modes of operation:

· No ping-pong support

Note:

- · Ping-pong buffer support for OUT Endpoint 0 only

- · Ping-pong buffer support for all endpoints

The ping-pong buffer settings are configured using the PPB1:PPB0 bits in the UCFG register.

The USB module keeps track of the ping-pong pointer individually for each endpoint. All pointers are initially reset to the Even BD when the module is enabled. After the completion of a transaction (UOWN cleared by the

Memory area not shown to scale.

SIE), the pointer is toggled to the Odd BD. After the completion of the next transaction, the pointer is toggled back to the Even BD and so on.

The Even/Odd status of the last transaction is stored in the PPBI bit of the USTAT register. The user can reset all ping-pong pointers to Even using the PPBRST bit.

Figure 17-7 shows the three different modes of operation and how USB RAM is filled with the BDs.

BDs have a fixed relationship to a particular endpoint, depending on the buffering configuration. The mapping of BDs to endpoints is detailed in Table 17-4. This relationship also means that gaps may occur in the BDT if endpoints are not enabled contiguously. This theoretically means that the BDs for disabled endpoints could be used as buffer space. In practice, users should avoid using such spaces in the BDT unless a method of validating BD addresses is implemented.

TABLE 17-4: ASSIGNMENT OF BUFFER DESCRIPTORS FOR THE DIFFERENT BUFFERING MODES

| or leaves omi |                 |            | BDs Assig    | ned to Endpo                     | int            |                     |

|---------------|-----------------|------------|--------------|----------------------------------|----------------|---------------------|

| Endpoint      | Mod<br>(No Ping |            |              | Mode 1<br>(Ping-Pong on EP0 OUT) |                | de 2<br>on all EPs) |

| tractica with | Out             | of fin reg | Out          | In                               | Out            | In                  |

| 0             | 0               | 1          | 0 (E), 1 (O) | 2                                | 0 (E), 1 (O)   | 2 (E), 3 (O)        |

| 1             | 2               | 3          | 3            | 4                                | 4 (E), 5 (O)   | 6 (E), 7 (O)        |

| 2             | 4               | 5          | 5            | 6                                | 8 (E), 9 (O)   | 10 (E), 11 (O)      |

| 3             | 6               | 7          | 7            | 8                                | 12 (E), 13 (O) | 14 (E), 15 (O)      |

| 4.56.         | 8               | 9          | 9            | 10                               | 16 (E), 17 (O) | 18 (E), 19 (O)      |

| 5             | 10              | 11         | 11           | 12                               | 20 (E), 21 (O) | 22 (E), 23 (O)      |

| 6             | 12              | 13         | 13           | 14                               | 24 (E), 25 (O) | 26 (E), 27 (O)      |

| 7             | 14              | 15         | 15           | 16                               | 28 (E), 29 (O) | 38 (E), 31 (O       |

| 8             | 16              | 17         | 17           | 18                               | 32 (E), 33 (O) | 34 (E), 35 (O       |

| 9             | 18              | 19         | 19           | 20                               | 36 (E), 37 (O) | 38 (E), 39 (O       |

| 10            | 20              | 21         | 21           | 22                               | 40 (E), 41 (O) | 42 (E), 43 (O       |

| 11            | 22              | 23         | 23           | 24                               | 44 (E), 45 (O) | 46 (E), 47 (O       |

| 12            | 24              | 25         | 25           | 26                               | 48 (E), 49 (O) | 50 (E), 51 (O       |

| 13            | 26              | 27         | 27           | 28                               | 52 (E), 53 (O) | 54 (E), 55 (O       |

| 14            | 28              | 29         | 29           | 30                               | 56 (E), 57 (O) | 58 (E), 59 (O       |

| 15            | 30              | 31         | 31           | 32                               | 60 (E), 61 (O) | 62 (E), 63 (O       |

Legend: (E) = Even transaction buffer, (O) = Odd transaction buffer

TABLE 17-5: SUMMARY OF USB BUFFER DESCRIPTOR TABLE REGISTERS

| Name                   | Bit 7       | Bit 6    | Bit 5                                     | Bit 4                                        | Bit 3                                       | Bit 2                                        | Bit 1 | Bit 0 |

|------------------------|-------------|----------|-------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------|-------|-------|

| BDnSTAT <sup>(1)</sup> | UOWN        | DTS      | PID3 <sup>(2)</sup><br>KEN <sup>(3)</sup> | PID2 <sup>(2)</sup><br>INCDIS <sup>(3)</sup> | PID1 <sup>(2)</sup><br>DTSEN <sup>(3)</sup> | PIDO <sup>(2)</sup><br>BSTALL <sup>(3)</sup> | BC9   | BC8   |

| BDnCNT <sup>(1)</sup>  | Byte Count  |          |                                           |                                              |                                             |                                              |       | -     |

| BDnADRL(1)             | Buffer Addr | ess Low  |                                           |                                              |                                             |                                              |       |       |

| BDnADRH(1)             | Buffer Addr | ess High |                                           |                                              |                                             |                                              |       |       |

Note 1: For buffer descriptor registers, n may have a value of 0 to 63. For the sake of brevity, all 64 registers are shown as one generic prototype. All registers have indeterminate Reset values (xxxx xxxx).

- 2: Bits 5 through 2 of the BDnSTAT register are used by the SIE to return PID3:PID0 values once the register is turned over to the SIE (UOWN bit is set). Once the registers have been under SIE control, the values written for KEN, INCDIS, DTSEN and BSTALL are no longer valid.

- Prior to turning the buffer descriptor over to the SIE (UOWN bit is cleared), bits 5 through 2 of the BDnSTAT register are used to configure the KEN, INCDIS, DTSEN and BSTALL settings.

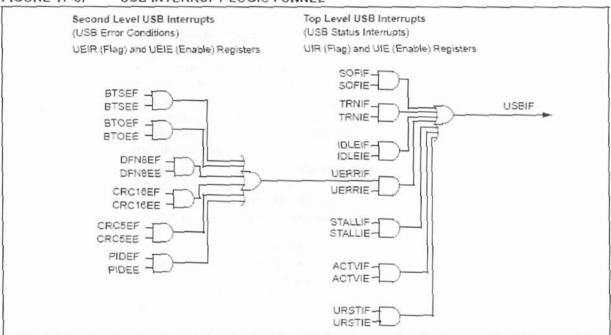

#### 17.5 USB Interrupts

The USB module can generate multiple interrupt conditions. To accommodate all of these interrupt sources. the module is provided with its own interrupt logic structure, similar to that of the microcontroller, USB interrupts are enabled with one set of control registers and trapped with a separate set of flag registers. All sources are funneled into a single USB interrupt request, USBIF (PIR2<5>), in the microcontroller's interrupt logic.

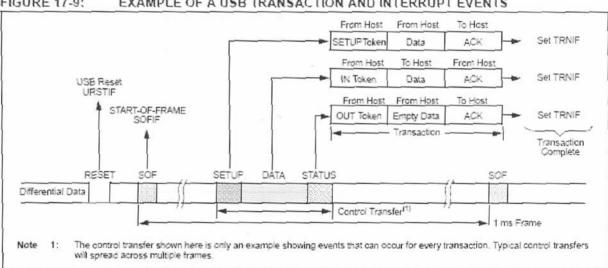

Figure 17-8 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the UIE and UIR registers, respectively. The second level consists of USB error conditions, which are enabled and flagged in the UEIR and UEIE registers. An interrupt condition in any of these triggers a USB Error Interrupt Flag (UERRIF) in the top level.

Interrupts may be used to trap routine events in a USB transaction. Figure 17-9 shows some common events within a USB frame and their corresponding interrupts.

FIGURE 17-8: USB INTERRUPT LOGIC FUNNEL

FIGURE 17-9: EXAMPLE OF A USB TRANSACTION AND INTERRUPT EVENTS

#### 17.5.1 USB INTERRUPT STATUS REGISTER (UIR)

bit 7 bit 6

bit 5

The USB Interrupt Status register (Register 17-7) contains the flag bits for each of the USB status interrupt sources. Each of these sources has a corresponding interrupt enable bit in the UIE register. All of the USB status flags are ORed together to generate the USBIF interrupt flag for the microcontroller's interrupt funnel.

Once an interrupt bit has been set by the SIE, it must be cleared by software by writing a '0'. The flag bits can also be set in software, which can aid in firmware debugging.

#### REGISTER 17-7: UIR: USB INTERRUPT STATUS REGISTER

|          |            | R/W-0     | R/W-0     | R/W-0    | R/W-0     | R-0                   | R/W-0  |

|----------|------------|-----------|-----------|----------|-----------|-----------------------|--------|

|          | SOFIF      | STALLIF   | IDLEIF(1) | TRNIF(2) | ACTVIF(3) | UERRIF <sup>(4)</sup> | URSTIF |

| bit 7    |            |           |           |          |           |                       | bit 0  |

| Unimplem | ontod. Doo | id so 'O' |           |          |           |                       |        |

- 1 = A START-OF-FRAME token received by the SIE

- 0 = No START-OF-FRAME token received by the SIE STALLIF: A STALL Handshake Interrupt bit

- 1 = A STALL handshake was sent by the SIE

- 0 = A STALL handshake has not been sent

- bit 4 IDLEIF: Idle Detect Interrupt bit<sup>(1)</sup>

- 1 = Idle condition detected (constant Idle state of 3 ms or more)

- 0 = No Idle condition detected

- bit 3 TRNIF: Transaction Complete Interrupt bit(2)

- 1 = Processing of pending transaction is complete; read USTAT register for endpoint information

- 0 = Processing of pending transaction is not complete or no transaction is pending

- bit 2 ACTVIF: Bus Activity Detect Interrupt bit (3)

- 1 = Activity on the D+/D- lines was detected

- 0 = No activity detected on the D+/D- lines

- bit 1 UERRIF: USB Error Condition Interrupt bit [4]

- 1 = An unmasked error condition has occurred

- 0 = No unmasked error condition has occurred

- bit 0 URSTIF: USB Reset Interrupt bit

- 1 = Valid USB Reset occurred; 00h is loaded into UADDR register

- 0 = No USB Reset has occurred

- Note 1: Once an Idle state is detected, the user may want to place the USB module in Suspend mode.

- Clearing this bit will cause the USTAT FIFO to advance (valid only for IN, OUT and SETUP tokens).

- This bit is typically unmasked only following the detection of a UIDLE interrupt event

- 4: Only error conditions enabled through the UEIE register will set this bit. This bit is a status bit only and cannot be set or cleared by the user.

| Legend:           |                  |                                         |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

# 17.5.2 USB INTERRUPT ENABLE STATUS REGISTER (UIE)

bit 7 bit 6

bit 5

bit 4

bit 3

bit 0

The USB Interrupt Enable register (Register 17-8) contains the enable bits for the USB status interrupt sources. Setting any of these bits will enable the respective interrupt source in the UIR register.

U-0

The values in this register only affect the propagation of an interrupt condition to the microcontroller's interrupt logic. The flag bits are still set by their interrupt conditions, allowing them to be polled and serviced without actually generating an interrupt.

R/W-0

R/W-0

R/W-0

#### REGISTER 17-8: UIE: USB INTERRUPT ENABLE REGISTER

R/W-0

R/W-D

|              | SOFIE         | STALLIE       | IDLEIE       | TRNIE        | ACTVIE | UERRIE | URSTIE |

|--------------|---------------|---------------|--------------|--------------|--------|--------|--------|

| bit 7        | ENHUR         | INTERROP      | T STATE      | N. K.E. INC. | •      | -      | bit 0  |

|              |               |               |              |              |        |        |        |

| Unimplem     | ented: Rea    | d as '0'      |              |              |        |        |        |

| SOFIE: ST    | ART-OF-FF     | RAME Token    | Interrupt Er | able bit     |        |        |        |

|              |               | E token inter |              | -            |        |        |        |

| 0 = START    | -OF-FRAM      | E token inter | rupt disable | d            |        |        |        |

| STALLIE:     | STALL Han     | dshake Inter  | rupt Enable  | bit          |        |        |        |

|              | interrupt er  |               |              |              |        |        |        |

| 0 = STALL    | interrupt di  | sabled        |              |              |        |        |        |

| IDLEIE: Idl  | e Detect In   | terrupt Enabl | e bit        |              |        |        |        |

| 1 = Idle det | tect interrup | t enabled     |              |              |        |        |        |

| 0 = Idle det | tect interrup | t disabled    |              |              |        |        |        |

| TRNIE: Tra   | Insaction C   | omplete Inte  | rrupt Enable | e bit        |        |        |        |

| 1 = Transa   | ction interru | pt enabled    |              |              |        |        |        |

R/W-0

R/W-0

bit 2 ACTVIE: Bus Activity Detect Interrupt Enable bit

1 = Bus activity detect interrupt enabled

0 = Bus activity detect interrupt disabled

bit 1 UERRIE: USB Error Interrupt Enable bit

1 = USB error interrupt enabled

0 = Transaction interrupt disabled

1 = USB error interrupt enabled 0 = USB error interrupt disabled URSTIE: USB Reset Interrupt Enable bit

1 = USB Reset interrupt enabled

0 = USB Reset interrupt disabled

-n = Value at POR

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'0' = Bit is cleared

x = Bit is unknown

"1" = Bit is set

#### 17.5.3 USB ERROR INTERRUPT STATUS REGISTER (UEIR)

The USB Error Interrupt Status register (Register 17-9) contains the flag bits for each of the error sources within the USB peripheral. Each of these sources is controlled by a corresponding interrupt enable bit in the UEIE register. All of the USB error flags are ORed together to generate the USB Error Interrupt Flag (UERRIF) at the top level of the interrupt logic.

Each error bit is set as soon as the error condition is detected. Thus, the interrupt will typically not correspond with the end of a token being processed.

Once an interrupt bit has been set by the SIE, it must be cleared by software by writing a '0'.

#### REGISTER 17-9: UEIR: USB ERROR INTERRUPT STATUS REGISTER

| R/C-0 | R/C-0  | R/C-0   | R/C-0  | R/C-0 | U-0              | U-U | R/C-0 |

|-------|--------|---------|--------|-------|------------------|-----|-------|

| PIDEF | CRC5EF | CRC16EF | DFN8EF | BTOEF | III <del>E</del> |     | BTSEF |

|       | CRC5EF | CRC16EF | DFN8EF | BTOEF | W <b>=</b>       |     | BTSEF |

| bit 7 | BTSEF: | Bit Stuff | Error | Flag | bit |

|-------|--------|-----------|-------|------|-----|

|-------|--------|-----------|-------|------|-----|

1 = A bit stuff error has been detected

0 = No bit stuff error

#### bit 6-5 Unimplemented: Read as '0'

bit 4 BTOEF: Bus Turnaround Time-out Error Flag bit

1 = Bus turnaround time-out has occurred (more than 16 bit times of Idle from previous EOP elapsed)

0 = No bus turnaround time-out

bit 3 DFN8EF: Data Field Size Error Flag bit

1 = The data field was not an integral number of bytes

0 = The data field was an integral number of bytes

bit 2 CRC16EF: CRC16 Failure Flag bit

1 = The CRC16 failed

0 = The CRC16 passed

bit 1 CRC5EF: CRC5 Host Error Flag bit

1 = The token packet was rejected due to a CRC5 error

0 = The token packet was accepted

bit 0 PIDEF: PID Check Failure Flag bit

1 = PID check failed

0 = PID check passed

| Legend:           |                   |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | C = Clearable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared | x = Bit is unknown |

# 17.5.4 USB ERROR INTERRUPT ENABLE REGISTER (UEIE)

The USB Error Interrupt Enable register (Register 17-10) contains the enable bits for each of the USB error interrupt sources. Setting any of these bits will enable the respective error interrupt source in the UEIR register to propagate into the UERR bit at the top level of the interrupt logic.

As with the UIE register, the enable bits only affect the propagation of an interrupt condition to the microcontroller's interrupt logic. The flag bits are still set by their interrupt conditions, allowing them to be polied and serviced with actually generating an interrupt.

#### REGISTER 17-10: UEIE: USB ERROR INTERRUPT ENABLE REGISTER

| R/W-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0  | R/W-0 |

|-------|-----|-----|-------|--------|---------|--------|-------|

| BTSEE | -   |     | BTOEE | DFN8EE | CRC16EE | CRC5EE | PIDEE |

| bit 7   | BTSEE: Bit Stuff Error Interrupt Enable bit                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------|

|         | 1 = Bit stuff error interrupt enabled<br>0 = Bit stuff error interrupt disabled                             |

| bit 6-5 | Unimplemented: Read as '0'                                                                                  |

| bit 4   | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit                                                   |

|         | 1 = Bus turnaround time-out error interrupt enabled<br>0 = Bus turnaround time-out error interrupt disabled |

| bit 3   | DFN8EE: Data Field Size Error Interrupt Enable bit                                                          |

|         | 1 = Data field size error interrupt enabled<br>0 = Data field size error interrupt disabled                 |

| bit 2   | CRC16EE: CRC16 Failure Interrupt Enable bit                                                                 |

|         | 1 = CRC16 failure interrupt enabled<br>0 = CRC16 failure interrupt disabled                                 |

| bit 1   | CRC5EE: CRC5 Host Error Interrupt Enable bit                                                                |

|         | 1 = CRC5 host error interrupt enabled<br>0 = CRC5 host error interrupt disabled                             |

| bit 0   | PIDEE: PID Check Failure Interrupt Enable bit                                                               |

|         | 1 = PID check failure interrupt enabled<br>8 = PID check failure interrupt disabled                         |

|         |                                                                                                             |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 17.6 USB Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are Bus Power Only, Self-Power Only and Dual Power with Self-Power Dominance. The most common cases are presented here.

#### 17,6.1 BUS POWER ONLY

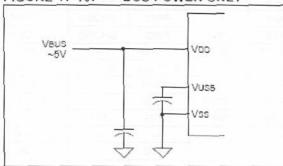

In Bus Power Only mode, all power for the application is drawn from the USB (Figure 17-10). This is effectively the simplest power method for the device.

FIGURE 17-10: BUS POWER ONLY

#### 17.6.2 SELF-POWER ONLY

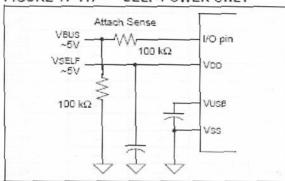

In Self-Power Only mode, the USB application provides its own power, with very little power being pulled from the USB. Figure 17-11 shows an example. Note that an attach indication is added to indicate when the USB has been connected.

FIGURE 17-11: SELF-POWER ONLY

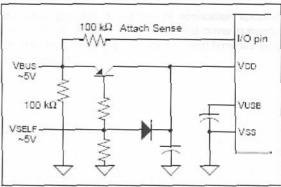

17.6.3 DUAL POWER WITH SELF-POWER DOMINANCE

Some applications may require a dual power option. This allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Figure 17-12 shows a simple Dual Power with Self-Power Dominance example, which automatically switches between Self-Power Only and USB Bus Power Only modes.

FIGURE 17-12: DUAL POWER EXAMPLE

Note: Users should keep in mind the limits for devices drawing power from the USB. According to USB Specification 2.0, this cannot exceed 100 mA per low-power device or 500 mA per high-power device.

#### 17.7 Streaming Parallel Port

The Streaming Parallel Port (SPP) is an alternate route option for data besides USB RAM. Using the SPP, an endpoint can be configured to send data to or receive data directly from external hardware.

This methodology presents design possibilities where the microcontroller acts as a data manager, allowing the SPP to pass large blocks of data without the microcontroller actually processing it. An application example might include a data acquisition system, where data is streamed from an external FIFO through USB to the host computer. In this case, endpoint control is managed by the microcontroller and raw data movement is processed externally.

The SPP is enabled as a USB endpoint port through the associated endpoint buffer descriptor. The endpoint must be enabled as follows:

- 1. Set BDnADRL:BDnADRH to point to FFFFh.

- Set the KEN bit (BDnSTAT<5>) to let SIE keep control of the buffer.

- Set the INCDIS bit (BDnSTAT<4>) to disable automatic address increment.

Refer to Section 18.0 "Streaming Parallel Port" for more information about the SPP.

- Note 1: If an endpoint is configured to use the SPP, the SPP module must also be configured to use the USB module.

Otherwise, unexpected operation may occur.

- In addition, if an endpoint is configured to use the SPP, the data transfer type of that endpoint must be isochronous only.

#### 17.8 Oscillator

The USB module has specific clock requirements. For full speed operation, the clock source must be 48 MHz. Even so, the microcontroller core and other peripherals are not required to run at that clock speed or even from the same clock source. Available clocking options are described in detail in Section 2.3 "Oscillator Settings for USB".

#### 17.9 USB Firmware and Drivers

Microchip provides a number of application specific resources, such as USB firmware and driver support. Refer to www.microchip.com for the latest firmware and driver support.

TABLE 17-6: REGISTERS ASSOCIATED WITH USB MODULE OPERATION(1)

| Name   | Bit 7    | Bit 6     | Bit 5               | Bit 4   | Bit 3    | Bit 2   | Bit 1  | Bit 0   | Details on page |

|--------|----------|-----------|---------------------|---------|----------|---------|--------|---------|-----------------|

| INTCON | GIE/GIEH | PEIEIGIEL | TMROIE              | INTOIE  | RBIE     | TMRBIF  | INTOIF | RBIF    | 51              |

| IPR2   | OSCFIP   | CMIP      | USBIP               | EEIP    | BOLIP    | HLVDIP  | TMR3IP | CCP2IP  | 54              |

| PIR2   | OSCFIF   | CMIF      | USBIF               | EEIF    | BCUF     | HLVDIF  | TMR3IF | CCP2IF  | 54              |

| PIE2   | OSCFIE   | CMIE      | USBIE               | EEIE    | BCLIE    | HLVDIE  | TMR3IE | CCP2IE  | 54              |

| UCON   |          | PPBRST    | SEG                 | PKTDIS  | USBEN    | RESUME  | SUSPND |         | 55              |